MaxPak® III High Speed Link Module M/N 57C424

# Industrial CONTROLS

Instruction Manual J2-3010 September, 1991

The information in this user's manual is subject to change without notice. Reliance Electric and its affiliates assumes no responsibility for errors that may appear in this user's manual.

## DANGER

ONLY QUALIFIED ELECTRICAL PERSONNEL FAMILIAR WITH THE CONSTRUCTION AND OPERATION OF THIS EQUIPMENT AND THE HAZARDS INVOLVED SHOULD INSTALL, ADJUST, OPERATE, AND/OR SERVICE THIS EQUIPMENT. READ AND UNDERSTAND THIS INSTRUCTION MANUAL AND APPROPRIATE MAXPAK III AND AUTOMAX DCS MANUALS IN THEIR ENTIRETY BEFORE PROCEEDING. FAILURE TO OBSERVE THIS PRECAUTION COULD RESULT IN SEVERE BODILY INJURY OR LOSS OF LIFE.

## WARNING

INSERTING OR REMOVING THIS MODULE OR ITS CONNECTING CABLES MAY RESULT IN UNEXPECTED MACHINE MOVEMENT. TURN OFF POWER BEFORE INSERTING OR REMOVING THE MODULE OR ITS CONNECTING CABLES. FAILURE TO OBSERVE THIS PRECAUTION COULD RESULT IN BODILY INJURY.

AutoMax<sup>™</sup> is a trademark of Reliance Electric Company or its subsidiaries. Reliance<sup>®</sup> and MaxPak<sup>®</sup> III are registered trademarks of Reliance Electric Company or its subsidiaries. MultiBus<sup>®</sup> is a registered trademark of Intel Corporation.

© Copyright Reliance Electric Company.

# **Table of Contents**

| 1.0 | INTR | ODUCT          | ION                                                 | 1-1  |

|-----|------|----------------|-----------------------------------------------------|------|

|     | 1.1  | Additio        | nal Information                                     | 1-3  |

|     | 1.2  |                | Hardware and Software                               |      |

|     | 1.3  | Conver         | tions                                               | 1-3  |

| 2.0 | MEC  | HANICA         | L/FUNCTIONAL DESCRIPTION                            | 2-1  |

|     | 2.1  | Mechar         | nical Description                                   | 2-1  |

|     | 2.2  | Functio        | nal Description                                     |      |

|     |      | 2.2.1          | 57C424 HSL Card Dual Port Register Map              |      |

|     |      |                | 2.2.1.1 Data Registers                              |      |

|     |      |                | 2.2.1.1.1 Receive Data Registers                    | 2-5  |

|     |      |                | 2.2.1.1.2 Transmit Data Registers                   | 2-5  |

|     |      |                | 2.2.1.2 Control Registers                           | 2-6  |

|     |      |                | 2.2.1.2.1 Communication/Status Registers            | 2-6  |

|     |      |                | 2.2.1.2.2 Configuration Registers                   | 2-10 |

|     |      | 2.2.2          | MaxPak III High Speed Link (HSL) Variables          |      |

|     |      | 2.2.3          | Sequence of Events                                  |      |

|     |      | 2.2.4          | MESSAGES                                            |      |

|     |      |                | 2.2.4.1 Message Control (L2_SCAN_PERIOD%)           | 2-18 |

|     |      |                | 2.2.4.1.1 AutoMax DCS to MaxPak III                 |      |

|     |      |                | Information Update Rate Calculations .              | 2-18 |

|     |      |                | 2.2.4.1.2 MaxPak III to AutoMax DCS                 |      |

|     |      |                | Information Update Rate Calculations .              | 2-20 |

|     |      | 2.2.5          | Timeout                                             | 2-22 |

|     |      | 2.2.6          | Tach Loss and Overspeed                             | 2-22 |

|     |      |                | 2.2.6.1 AutoMax Rack Receiving Speed Feedback       |      |

|     |      |                | 2.2.6.2 MaxPak III Drive Receiving Speed Feedback   |      |

|     |      | 2.2.7          | Data/Link Integrity                                 | 2-24 |

| 3.0 | INST |                | ON                                                  |      |

|     | 3.1  |                |                                                     |      |

|     |      |                |                                                     |      |

|     | 3.3  | Module         | e Replacement                                       | 3-3  |

| 4.0 | PRO  | GRAM           | 1ING                                                | 4-1  |

|     | 4.1  |                | k III HSL Registers                                 |      |

|     | 4.2  | -              | peed Link (HSL) Configuration Map                   |      |

|     | 4.3  |                | bad Requirements                                    |      |

|     |      | 4.3.1          | Statement Syntax                                    |      |

|     |      | 4.3.2          | Statement Position Within Source Configuration File |      |

|     |      | 4.3.3          | HSL Table Requirements                              |      |

|     |      | 4.3.4          | MaxPak III Drive Requirements                       |      |

|     |      | 4.3.5<br>4.3.6 | Integer Input Registers                             |      |

|     |      | 4.3.0<br>4.3.7 | Integer Output Registers                            |      |

|     |      | 4.3.8          | Boolean Output Registers                            |      |

|     |      |                |                                                     | · •  |

|     | 4.4<br>4.5 | Minimum System Configuration4-9High Speed Link Configuration Program Examples4-94.5.1Example #14-104.5.2Example #24-15 | 0 |

|-----|------------|------------------------------------------------------------------------------------------------------------------------|---|

| 5.0 | MES        | SAGE COMMUNICATION ERRORS                                                                                              |   |

|     | 5.1        | Message Verification Errors 5-1                                                                                        |   |

|     | 5.2        | Transmit Overlap Errors 5-1                                                                                            |   |

|     |            | 5.2.1 AutoMax DCS to MaxPak III Drive Transmit Overlap 5-1                                                             |   |

|     |            | 5.2.2 MaxPak III Drive to AutoMax DCS Transmit Overlap 5-2                                                             |   |

|     | 5.3        | Receive Overlap Errors 5-2                                                                                             |   |

|     |            | 5.3.1 AutoMax DCS Receive Overlap 5-2                                                                                  |   |

|     |            | 5.3.2 MaxPak III Drive Receive Overlap 5-3                                                                             |   |

|     | 5.4        | Timeout                                                                                                                |   |

|     |            | 5.4.1 AutoMax to MaxPak III Drive Timeout                                                                              |   |

|     |            | [(2 x AutoMax DCS Scan Period) + 10] 5-3                                                                               |   |

|     |            | 5.4.2 MaxPak III to AutoMax Timeout                                                                                    |   |

|     |            | [(2 x MaxPak III's L2_SCAN_PERIOD%) + 5] 5-4                                                                           |   |

|     | 5.5        | Message Not Received Errors 5-4                                                                                        |   |

|     | 5.6        | Invalid Operation Errors 5-4                                                                                           |   |

| 6.0 | CON        | FIGURATION ERRORS 6-1                                                                                                  |   |

| 7.0 | TRO        | OUBLESHOOTING                                                                                                          |   |

.

# Appendices

| Appendix A –<br>Default HSL Register Map Assignments A:1                 |

|--------------------------------------------------------------------------|

| Appendix B –<br>7-Segment LED Display Codes                              |

| Appendix C –<br>Interrupt Status and Control Register Layout (REG 0) C:1 |

| Appendix D -<br>RS-232 Wiring Characteristics D:1                        |

| Appendix E –<br>57C424 Technical Specifications E:1                      |

| Appendix F –<br>HSL Fatal Error Codes for the 57C424 F:1                 |

| Appendix G -<br>Verify Errors (Detected during verify stage) G:1         |

| Appendix H –<br>DownLoad Errors (Protected during the download stage)    |

| Appendix J –<br>Procedure for Configuring/Re-Configuring HSL Link        |

| Appendix K –<br>Overview of High Speed Link (HSL) Functionality          |

| Index l:1                                                                |

# **List of Figures**

| Figure 1-1 - MaxPak III High Speed Link System                                              | 1-1 |

|---------------------------------------------------------------------------------------------|-----|

| Figure 2.1 – HSL Module Faceplate<br>Figure 2-2 – Typical MaxPak III-to-AutoMax Connections |     |

| Figure 4.1 - HSL Configuration Map                                                          | 4-3 |

# **List of Tables**

|             | AutoMax DCS -> MaxPak III Drive Message Composition 2-19<br>MaxPak III Drive -> AutoMax DCS Message Composition 2-2 |  |

|-------------|---------------------------------------------------------------------------------------------------------------------|--|

| Table 3-1 - | MaxPak III Comm Port HSL Channel Selection                                                                          |  |

.

# **1.0 INTRODUCTION**

The products described in this instruction manual are manufactured and distributed by Reliance<sup>®</sup> Electric Industrial Company.

- Note: This instruction manual assumes the following regarding user knowledge:

- 1. The user has complete familiarity with the MaxPak III drive, and has read the applicable documentation provided with the drive.

- The user has complete familiarity with the AutoMax DCS system, and has read the applicable documentation provided with the system.

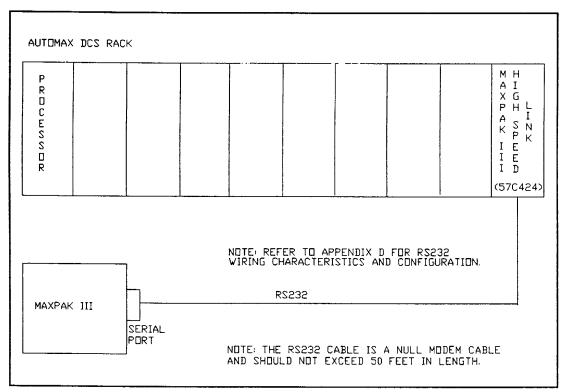

The High Speed Link (HSL) module is a point-to-point real time control Input/Output (I/O) channel (or communications link) that provides communication between the MaxPak III Digital D-C Drive (MaxPak III) and the AutoMax Distributed Control System (DCS) Industrial Controller. See Figure 1-1.

## Figure 1-1 - MaxPak III High Speed Link System

The HSL module can be used in applications where the AutoMax system closes an outer regulation loop and then passes information to an inner loop on the MaxPak III drive (see section 4.5 of this manual for program examples). Hence, the MaxPak III High Speed Link system provides a standard hardware configuration for a variety of applications.

## **HSL Module**

The HSL module is designed to fit into the AutoMax Multibus rack. Its dual port memory (see Section 2.2.1) passes status, sequencing, and regulation information along the link via an RS-232 medium at 41.6 Kbaud.

Status, sequencing, and regulation information are passed along the link from the HSL module's dual port memory map (see section 4.2 of this manual) using a customized message protocol. This is a master-slave communication with the HSL module being the master and the MaxPak III drive being the slave except for on-line update messages. The HSL module initiates the transmit messages for the three basic commands for a message to be sent to the MaxPak III drive. These three basic commands are:

- Configuration request

- Change mode request: go to on-line or go to off-line

- Update request: off-line update or on-line update

These commands are to be issued by the user or the configuration program writing the appropriate value to command register (Register 30). (See section 2.2.1.2 of this manual for further details.)

The configuration registers (40 thru 45, and 70 thru 81) are to be written by the user or the application program prior to issuing the configuration request to Register 30. These registers determine the size of the messages to/from the MaxPak III, the update message scan time and the update message timeout. (See section 4.4 of this manual for the minimum HSL module and MaxPak III drive configuration.)

## MaxPak III

Variables to be sent to/received from the MaxPak III drive are assigned dual port addresses on the HSL module and are assigned using the IODEF statement (Reference Instruction Manual J-3675 for structuring IODEF statements) in an AutoMax Configuration Task. Moreover, the variables to be used in the AutoMax Configuration Task must exist in the MaxPak III drive's configuration. (Reference section 4.5 of this manual for program examples.)

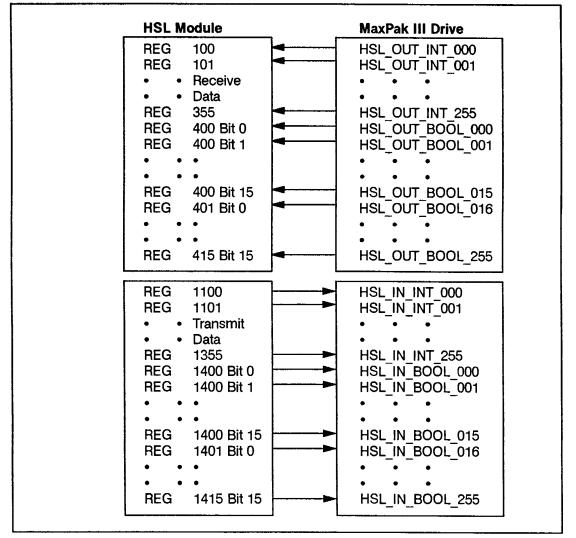

There are a total of 512 integer registers (HSL\_OUT\_INT\_\* and HSL\_IN\_INT\_\*); 256 for each type that can be communicated between the AutoMax controller and the MaxPak III drive. Simarly, there are a total of 512 boolean registers (HSL\_OUT\_BOOL\_\* and HSL\_IN\_BOOL\_\*); 256 for each type. However, the number and type of variables are completely configurable by the user via the HSL module configuration registers. Note that the constraints on the number of variables are limited according to the number of variables in the MaxPak III drive's configuration.

The MaxPak III drive transmits acknowledge messages to the HSL module for the three basic commands described previously. The acknowledge message formats correspond to the three basic commands.

# 1.1 Additional Information

You must become familiar with the instruction manuals which describe your system configuration. This may include, but is not limited to, the following:

- J-3649 DCS 5000/AutoMax Configuration Task Instruction Manual

- J-3630 AutoMax Programming Executive Instruction Manual

- J-3675 AutoMax Enhanced Basic Language Instruction Manual

- J-3676 AutoMax Control Block Language Instruction Manual

- J-3677 AutoMax Ladder Logic Language Instruction Manual

- D2-3203 MaxPak III Drive Version 6 Instruction Manual

# 1.2 Related Hardware and Software

- MaxPak III Digital D-C Drive

- MaxPak III Digital D-C Drive Version 6.1A or Higher Operating Software

- RS-232 Serial Cable

- HSL Module (M/N 57C424)

- AutoMax DCS

The HSL Module must use the MaxPak III Digital D-C Drive Version 6.1A or higher software for proper operation. If the drive was shipped from the factory without a custom ordered or Engineering Sales ordered configuration, the Version 6.1A software should contain a default HSL assignment register map in the MaxPak III drive's configuration file (see Appendix A).

It is recommended to upload the configuration file and save to disk for reference prior to making changes to the existing configuration file. If overwritten, the existing configuration file will be lost.

# 1.3 Conventions

- Bit 15 is the most significant bit in a word. This applies to both the HSL Module and the MaxPak III drive references to bit positions in this document.

- While the MaxPak III drive is Off-line (SYS\_ONLINE@=OFF), the user has access to all drive input variables with access levels of 0 through 5 which are defined in the HSL map. Output variables are always accessible.

- While the MaxPak III drive is On-line (SYS\_ONLINE@=ON), the user has access to drive input variables with access levels of 0 through 2 which are defined in the HSL map.

- One (1) tick is equivalent to 0.5 ms for the AutoMax DCS message scan period. Note that this product employs variable tick rates at 0.5 ms/tick.

The remainder of this manual describes the functions and specifications of the module. It also includes a detailed overview of installation and troubleshooting procedures, as well as examples of configuration.

# 2.0 MECHANICAL/FUNCTIONAL DESCRIPTION

The following sections describe the mechanical and functional characteristics of the HSL module.

# 2.1 Mechanical Description

The HSL module is an electronic module (printed circuit assembly) that plugs into the AutoMax DCS rack. This printed circuit assembly has an RS-232 port for communicating with the MaxPak III Digital D-C Drive.

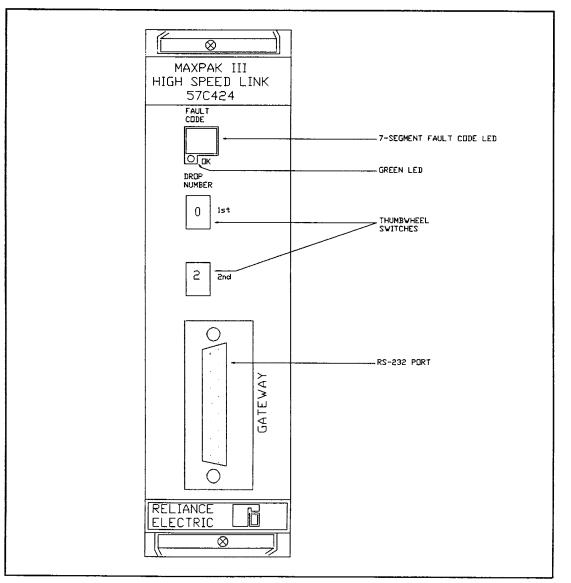

The faceplate of the module contains a 7-segment LED, a green LED, two thumbwheel switches, and one electrical connector. See Figure 2-1.

Figure 2.1 – HSL Module Faceplate

The 7-segment LED is labeled "FAULT CODE". This 7-segment LED is used to display card status. Refer to Appendix B for the 7-segment LED Display Codes.

A green LED, labeled "OK", is used to indicate whether the HSL module is functioning properly.

Two thumbwheel switches (labeled "1ST" and "2ND") are present but are used only for factory burn-in testing.

One electrical connector labeled "GATEWAY" is used for transmitting and receiving data to/from a MaxPak III Digital D-C Drive.

This module is also equipped with card ejectors to allow easy removal from the AutoMax DCS rack. Hold down screws are provided to secure the module in the rack.

The printed circuit board assembly has a rugged plastic housing to protect both the component and foil sides. The rear edge connector is shrouded by an enclosure to further protect the card from handling damage.

# 2.2 Functional Description

The remainder of this chapter covers the following topics:

- 57C424 HSL Card Dual Port Register Map

- MaxPak III High Speed Link (HSL) Variables

- Sequence of Events

- Messages

- Timeout

- Tach Loss and Overspeed

- Data Integrity

# 2.2.1 57C424 HSL Card Dual Port Register Map

The 57C424 HSL Card Dual Port Register Map consists of Control Registers, (Configuration Registers and Communication/Status Registers) and Data Registers (Receive and Transmit). The following outlines the Read/Write (R/W) function of the registers. An explanation of each register follows in the succeeding paragraphs.

**Note:** Not all the registers shown in the dual port register map are contiguous (Registers not specified in this map are not accessible. Any access attempts will result in a bus error.)

# **Serial Link Statistics**

| REGISTER 13:       Keyswitch State       (F         REGISTER 14:       Messages Received       (F         REGISTER 15:       Receive Timeouts       (F         REGISTER 15:       Receive Timeouts       (F         REGISTER 16:       Checksum Errors       (F         REGISTER 17:       Overrun Errors       (F         REGISTER 18:       Framing Errors       (F         REGISTER 19:       Messages Transmitted       (F         REGISTER 20:       Parity Errors       (F | Register 15:<br>Register 16:<br>Register 17:<br>Register 18:<br>Register 19: | Receive Timeouts       Checksum Errors         Checksum Errors       Checksum Errors         Framing Errors       Checksum Errors         Messages Transmitted       Checksum Errors | (R)<br>(R)<br>(R)<br>(R)<br>(R)<br>(R) |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

#### Link Status

| Link Active                | (R)                                                                                                                 |

|----------------------------|---------------------------------------------------------------------------------------------------------------------|

| Communications Error Flags | (R)                                                                                                                 |

| Configuration Error Flags  | (R)                                                                                                                 |

| MaxPak III Status Byte     | (R)                                                                                                                 |

| Transmit Active            | (R)                                                                                                                 |

|                            | Link Active<br>Communications Error Flags<br>Configuration Error Flags<br>MaxPak III Status Byte<br>Transmit Active |

#### Commands

| REGISTER 0:  | Status & Control Register 0 | (R/W) |

|--------------|-----------------------------|-------|

| REGISTER 30: | COMMAND/STATUS CHANGE       | (R/W) |

|              | Communication ERROR reset   |       |

# MaxPak III Variable Map Data

| REGISTER 40: | Total input On-Line integer Registers (R)  |

|--------------|--------------------------------------------|

| REGISTER 41: | Total input Off-Line integer Registers (R) |

| REGISTER 42: | Total input On-Line boolean bits (R)       |

| REGISTER 43: | Total input Off-Line boolean bits (R)      |

| REGISTER 44: | Total output integer Registers (R)         |

| REGISTER 45: | Total output boolean bits (R)              |

## Link Device Data

| Fatal Error #               | (R)                                                                                                                                                                                    |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HSL Comm Card ASCII ID 'HS' | (R)                                                                                                                                                                                    |

|                             |                                                                                                                                                                                        |

|                             |                                                                                                                                                                                        |

|                             | Fatal Error #       HSL Comm Card ASCII ID 'HS'         HSL Comm Card ASCII ID 'L'       HSL Comm Card ASCII ID 'L'         MaxPak III Version Number       HSL Comm Card ASCII ID 'L' |

# Data to MaxPak III Configuration

| REGISTER 70: | Number of integer registers to |       |

|--------------|--------------------------------|-------|

|              | transmit to the MaxPak III     | (R/W) |

| REGISTER 71: | Number of boolean bits to      | • •   |

|              | transmit to the MaxPak III     | (R/W) |

.

# Data from MaxPak III Configuration

| REGISTER 75: | Number of integer registers to    |       |

|--------------|-----------------------------------|-------|

|              | receive from MaxPak III           | (R/W) |

| REGISTER 76: | Number of boolean bits to receive | · ·   |

|              | from MaxPak III                   | (R/W) |

# Link configuration

| REGISTER 80: | Maximum receive TIMEOUT (msec) (R/W) |

|--------------|--------------------------------------|

| REGISTER 81: | Speed loop time period               |

|              | (ticks: 1 = 0.5msec) (R/W)           |

# Input Integer registers (from MaxPak III drive)

| REGISTER 100:      | Data Receive Integer Register 0 (R)                                                 |

|--------------------|-------------------------------------------------------------------------------------|

| REGISTER 101:      | Data Receive Integer Register 1 (R)                                                 |

| REGISTER 102:      | Data Receive Integer Register 2 (R)                                                 |

|                    |                                                                                     |

| •                  | •                                                                                   |

| •<br>REGISTER 354: | •<br>Data Receive Integer Register 254 (R)<br>Data Receive Integer Register 255 (R) |

# Input booleans (from MaxPak III drive)

| <b>REGISTER 400:</b> | Data Receive Packed  |                     |

|----------------------|----------------------|---------------------|

|                      | boolean register #0  | (R)                 |

| REGISTER 401:        | Data Receive Packed  | ``                  |

|                      | boolean register #1  | (R)                 |

| •                    | •                    | • •                 |

| REGISTER 415:        | Data Receive Packed  | <i>(</i> <b>_</b> ) |

|                      | boolean register #15 | (R)                 |

# Output registers (to MaxPak III drive)

| REGISTER 1101: Data      | a Transmit Integer Register 0                                       | (R/W) |

|--------------------------|---------------------------------------------------------------------|-------|

| REGISTER 1102: Data      | Transmit Integer Register 2                                         | (R/W) |

|                          |                                                                     |       |

| •                        | •                                                                   |       |

| •<br>REGISTER 1354: Data | •<br>Transmit Integer Register 254<br>Transmit Integer Register 255 | (R/W) |

# Output booleans (to MaxPak III drive)

| REGISTER 1400: Data Transmit Packed |    |

|-------------------------------------|----|

| boolean register #0                 | N) |

| REGISTER 1401: Data Transmit Packed | ,  |

| boolean register #1                 | N) |

| • •                                 | '  |

| REGISTER 1415: Data Transmit Packed |    |

| boolean register #15 (R/V           | N) |

|                                     | ,  |

.

## 2.2.1.1 Data Registers

The data registers are divided into two parts. Receive Data Registers – from the MaxPak III drive to the HSL module and Transmit Data Registers – from the HSL module to the MaxPak III drive. The registers from 100 to 1415 are assigned for the data registers.

## 2.2.1.1.1 Receive Data Registers

**REGISTERS 100–101** – These are the "high priority" integer data receive registers 0–1. The HSL module will generate a Multibus interrupt (if so enabled) immediately upon receipt and validation of these registers. These registers are guaranteed to be sent by the MaxPak III drive every L2\_SCAN\_PERIOD%. They are the first registers transmitted in each message and the first registers received. The rest of the received message will still be in transit when these registers are updated (see sections 2.2.4.1.2, and 4.1 for details). Immediately following the update, the HSL module asserts the multibus interrupt, if enabled. (See APPENDIX C for details on Multibus interrupt enable and disable.) Then the application would normally read Registers 100 and 101. In this way, the application may be synchronized to the MaxPak III drive.

**REGISTERS 102 to 355** – These are the remaining data registers that may be used to receive miscellaneous integer data from the MaxPak III drive (receive registers 2 through 255). Registers 102 to 355 are not guaranteed to be received every L2\_SCAN\_PERIOD%. Depending on the number of registers being sent, it may take several scans to send all the data.

**REGISTER 400** – Data Receive Boolean bits, register #0. This register is guaranteed to be sent every L2\_SCAN\_PERIOD%, but is not high priority (i.e. it does not generate a Multibus interrupt). Thus, it is normal receive data that must be verified separately and its value may take longer to appear in this register after being received than the high priority data. If less than 16 bits are to be sent to the HSL module (REGISTER 76), only those bits requested will be updated.

**REGISTERS 401 to 415** – These Boolean bit registers are for miscellaneous boolean data from the MaxPak III drive. They are not guaranteed to be received every L2\_SCAN\_PERIOD%. Depending on the number of registers being sent, it may take several L2\_SCAN\_PERIOD% to send all the data. If the number of boolean bits to be received by the HSL module is  $\leq$  16 (REGISTER 76), these registers are not updated.

## 2.2.1.1.2 Transmit Data Registers

**REGISTER 1100** – High priority transmit register. The contents of this register are written to the associated MaxPak III variable immediately upon receipt and validation, without waiting for receipt of the remainder of the update message. The AutoMax DCS Processor will typically write the current minor loop reference (or some other high priority datum) to be passed to the MaxPak III drive in this register.

**REGISTERS 1101 to 1355** – These are the remaining data registers that may be used to transmit miscellaneous data to MaxPak III HSL integer input registers 1 through 255. The time to send all these registers will vary depending on the total number of registers to be sent and the message scan period (ticks) (see Register 81 in Section 2.2.1.2.2). Several registers are sent each message.

**REGISTER 1400** – The data in this register is defined to be booleans, or bit flags, to be set/reset by the application as it wishes. These 16 boolean bits will be sent to the MaxPak III every time the AutoMax DCS application program issues a transmit request. Examples of use include SEQ\_DRIVE\_EN@, SEQ\_JOG@, SEQ\_RUN@, SEQ\_STOP\_ILIM@, etc.

**REGISTER 1401 to 1415** – These are the remaining registers that will be used to transmit miscellaneous boolean data to the MaxPak III drive. If the number of boolean bits to send is  $\leq$  16 (REGISTER 71), these registers will not be used. The time to send these registers will vary depending on the total number of registers (16 booleans/register) to be sent and the # of ticks in the speed loop task (REGISTER 81).

# 2.2.1.2 Control Registers

The Control Registers are generally divided into two parts. One is the communication/status related control registers (Registers 0 thru 31). The other is the configuration related registers (Registers 40 thru 45 and 70 thru 81).

# 2.2.1.2.1 Communication/Status Registers

**REGISTER 0** – (Interrupt Status & Control REGISTER 0). This register is used to support AutoMax DCS hardware for Multibus interrupt.

This register is specified in an IODEF statement (see the Reliance AutoMax Basic Programming Reference, I/M #J-3600-1, for a description of the IODEF statement). The name assigned in the IODEF is used in defining a hardware event on the AutoMax DCS processor card. This feature is used to synchronize the AutoMax DCS processor card with feedback being sent by the MaxPak III drive (i.e. Speed Feedback). See APPENDIX C for REGISTER 0 layout.

(Note: An AutoMax DCS 57C430A processor (not DCS 5000) or later processor must be used if interrupt capability is desired.)

**REGISTER 4** – (Link active) Bit 0 is set (1) if the HSL module is receiving messages and a valid configuration has been acknowledged by the MaxPak III. Bit 0 is reset (0) if the HSL module is not receiving messages. Also, a 'C' will appear on the 7 segment led if the HSL module is NOT receiving messages.

**REGISTER 13** – (Keyswitch state) Value representing the state of the keyswitch on the AutoMax processor board.  $0, \geq 4$ : CARD IN BURN-IN OVEN, 1:NORMAL (MEMORY PROTECT), 2: SETUP, 3: PROGRAM. Program mode is monitored constantly and will reflect a keyswitch change anytime.

**REGS 14-20** – Counters for communication statistics. These values are updated when appropriate by the HSL module.

**REGISTER 26** – This register latches the five types of communication errors that can occur. Note: The five errors defined for Register 26 are first fault errors. In other words, when any one of the errors occur it is latched and its respective bit is set in Register 26 (along with bit 15). No further errors can be latched until this error is cleared (See Register 31). This allows the user to determine which error occurred first,

BIT 0 (Receive TIMEOUT Error) – Bit 0 is set if the AutoMax DCS does not receive a message within the timeout period specified by REGISTER 80. When set, it will remain set until the AutoMax DCS application issues an error reset, REGISTER 31. (See section 2.2.1.1 for details). If the link is not active (Register 4 = 0), an error reset will have no effect. Also, if Register 26 is non-zero, no messages will be transmitted to the MaxPak III drive.

BIT 1 (Transmit Command OVERLAP Error) – Bit 1 is set if the AutoMax Processor writes a value to REGISTER 30 (the transmit message command) before the transmission of the previous message is complete. When set, it will remain set until the AutoMax DCS application issues an error reset, REGISTER 31 (See section 2.2.1.1 for details).

BIT 2 (Receive OVERLAP Error) – Bit 2 is set if the HSL module receives more than 2 new messages before it is finished processing the last received message. When set, it will remain set until the AutoMax DCS application issues an error reset, REGISTER 31 (See section 2.2.1.1 for details).

BIT 3 (Message Not Received Error) – Bit 3 is set if a configure, a status change (Off-Line to On-Line and vice-versa) or an Off-Line update is sent to the MaxPak III drive and no acknowledgement is received. When set, it will remain set until the AutoMax DCS application issues an error reset via REGISTER 31. If the MaxPak III drive is not running (SEQ\_ARM\_ACTIVE@ = OFF) and the HSL module is waiting on an acknowledge message from the MaxPak III drive, a timeout will not set this error latch immediately. The HSL module will send two retries of the same command message. If no acknowledgement before the third message is received, the timeout latch will be set.

BIT 4 (Invalid Operation) – HSL module attempted an invalid operation while the MaxPak III armature was active. Invalid operations include:

a) attempting to send a go off-line command

b) attempting to send a configure command

When set, it will remain set until the AutoMax DCS application issues an error reset, REGISTER 31.

BIT 15 (Global Communication Error) – This bit is set when any of the other Register 26 bits are set. (The logical 'OR' of Register 26 bits 0 to 14.)

**REGISTER 27** – Configuration error flags. These flags will reflect the dynamic state of configuration status. Below is a list of errors that could occur and the bits that correspond to them:

B0 = Number of On-Line integer registers to be received from the MaxPak III drive is out of range of the MaxPak III drive's defined integer map (i.e. REGISTER 75 is too big).

B1 = Number of On-Line boolean bits to be received from the MaxPak III is out of range of the MaxPak III drive's defined booleans map (i.e. REGISTER 76 is too big).

B2 = MaxPak III drive and HSL module software revisions are incompatible.

B3 = Number of On-Line integer registers to be sent to the MaxPak III is out of range of the MaxPak III drive's defined integer register map (i.e. REGISTER 70 is too big).

B4 = Number of On-Line boolean registers to be sent to the MaxPak III is out of range of the MaxPak III drive's defined booleans map (i.e. REGISTER 71 is too big).

$B5 = One \text{ or more configuration registers (70 to 81) is out of range from the default limits (see register descriptions for default limits).$

B6 - B14 = Currently not defined

B15 = Global Configuration Error bit. This bit is set if any of the other Register 27 bits are set. (The logical 'OR' of Register 27 bits 0 - 14.)

When B15 is set, no messages will be sent from the HSL module to the MaxPak III drive. Once the user corrects his configuration error, this bit will be reset and message transmission may commence. It is up to the application to control the message sequence to restart the link. The HSL module will not modify values in REGISTERS 70 – 81 so that the user may see which REGISTER is in error.

**REGISTER 28** - (MaxPak III Status Byte) This register is used to store booleans describing the current state of the MaxPak III drive. All messages received from the MaxPak III drive include this data automatically. Defined bits are as follows:

- B7 = State of SEQ\_ARM\_ACTIVE@

- B6 = State of SYS\_SHUTDOWN@

- B5 = State of SYS\_INIT\_FAIL@

Note: If bit 5 or bit 6 of Register 28 is non-zero, the drive is off-line.

**REGISTER 29** – (Transmit active) When bit 0 of this register is set to 1, the HSL module is sending data to the MaxPak III drive. This register may be tested before a TRANSMIT COMMAND is given (via REGISTER 30) in order to prevent transmit OVERLAP errors.

**Note:** There is a maximum 500 uSec processing delay in recognizing the command in Register 30. Therefore, the transmit active flag goes true after a maximum of 500 uSec with respect to the command in Register 30.

**REGISTER 30** – (COMMAND/STATUS CHANGE) This register is used for several purposes outlined below. Commands are issued by the user (or application task) writing the appropriate value to this register as follows:

- 2 = Go Off-line

- 3 = Go On-line

- 4 = Reconfigure

- 128 = Update Request (send message)

Note: All write access to this register must be 16 bits wide. For example, this sequence is correct: IODEF CMD REG%[SLOT = 5, REGISTER = 30] CMD REG% = 4 whereas, this is not:

IODEF RECONFIGURE@[SLOT = 5, REGISTER = 30, BIT = 2] ٠

RECONFIGURE@=ON

Command 2 - This instructs the MaxPak III drive to go off-line.

Command 3 - This instructs the MaxPak III drive to go on-line.

Command 4 - This command is issued after the user makes a change to any of the configuration REGISTERS 70, 71, 75, 76, 80, or 81. Issuing this command after the change to these registers inform the MaxPak III of the change by sending it a message to that effect. NOTE: This can only be done while the MaxPak III is not running (SEQ ARM ACTIVE@ = OFF).

Command 128 - Update request. When this command is issued and no bits are set in REGISTER 26, REGISTER 27 or REGISTER 29, the HSL module will transmit the integers in dual port starting with data REGISTER 1100 and the booleans in dual port starting with data REGISTER 1400. Immediately after starting the transmit process, the HSL module will clear the command register, but this does not mean that the transfer of data is complete. For that information, monitor TRANSMIT ACTIVE REGISTER 29 for a true to false transition

When a command is detected, and no communication and/or configuration errors are present (REGISTERS 26 AND 27 respectively) the HSL module immediately clears the command register and sets transmit active (REGISTER 29 Bit 0). After that, the message will be sent. This permits the HSL module to detect an overlap condition which may occur when transmit active is set and a new command is issued.

The command register should be checked prior to writing a value to it to insure that no previous request is pending. The command register is checked by performing a logical "AND" of its contents with Hexidecimal 0086. If the result is non-zero, a new request should not be written

REGISTER 31 - (ERROR RESET COMMAND) A false-to-true transition will clear all communication errors with the exception of a timeout. If, and only if, the link active bit is set (REGISTER 4 bit 0), error reset will also clear the timeout error. REGISTER 31 bit 0 must be held high for at least 50ms to insure the reset is seen by the HSL module. The HSL module will not write to this bit. Control of its value is given solely to the AutoMax processor card.

## 2.2.1.2.2 Configuration Registers

Configuration registers are used to tailor the HSL to the users needs. Each register controls a specific aspect of the communication. Each register must be verified to insure its value is acceptable. Default values for registers 70, 71, 75, 76, 80, and 81 are initialized by the HSL module at powerup or on a "Stop All" command. Some variables can be verified locally, others must be checked remotely.

Configuration is accomplished by writing the correct values to registers 70 - 81 and then writing a 4 to Register 30 (provided Registers 26 and 29 read 0).

The HSL may be configured when the MaxPak III drive is on-line or off-line. If the MaxPak III drive is on-line, the armature must not be active (SEQ\_ARM\_ACTIVE@ = OFF).

If the user tries to configure the MaxPak III drive while on-line and the armature is active, a configuration error results and is shown in REGISTER 27 bit 4. A command to go off-line will also cause this error. See REGISTER 27 for information on the Configuration Errors Register.

Both the MaxPak III drive and HSL module verify the configuration requested against their own internal variables to decide whether the new configuration is valid or not. If the configuration selected on one side conflicts with the configuration on the other side, a configuration error results and is shown in REGISTER 27. See REGISTER 27 for information on the Configuration Errors Register.

For instance, if the user wants to set the number of integer registers to transmit to the MaxPak III drive, the user places the value in REGISTER 70 and checks the MaxPak III status to insure it is not running (i.e. SEQ\_ARM\_ACTIVE@ = OFF, see REGISTER 28). If it is, the user must stop the drive with an update command before a configure is allowed.

After checking the status again to insure the MaxPak III drive is not running, the user would then send the configure command. If the MaxPak III drive determines if more integers have been requested than are defined in its HSL module register map, a configuration error results and is shown in REGISTER 27. See REGISTER 27 for information on the Configuration Errors Register.

**REGISTER 40** – (Total input on-line integer registers) This value represents the number of input integers the MaxPak III drive has defined in its HSL register map which have an access level of 2 or less. It is provided so the user may read this register and determine the largest value permitted in REGISTER 70 that will guarantee a successful configure IF THE MaxPak III DRIVE IS ON-LINE.

**REGISTER 41** – (Total input off-line integer registers) This value represents the number of input integers the MaxPak III drive has defined in its HSL register map which have an access level of 3 or more. It is provided so the user may read this register, add its value to the value read in REGISTER 41 (on-line integers) and determine the largest value permitted in REGISTER 70 that will guarantee a successful configure IF THE MaxPak III DRIVE IS OFF-LINE.

**REGISTER 42** – (Total input on-line boolean bits) This value represents the number of input boolean bits the MaxPak III drive has defined in its HSL register map which have an access level of 2 or less. It is provided so the user may read this register and determine the largest value permitted in REGISTER 71 that will guarantee a successful configure IF THE MaxPak III DRIVE IS ON-LINE.

**REGISTER 43** – (Total input off-line boolean bits) This value represents the number of input boolean bits the MaxPak III drive has defined in its HSL register map which have an access level of 3 or more. It is provided so the user may read this register add its value to the value read in REGISTER 42 (on-line booleans) and determine the largest value permitted in REGISTER 71 that will guarantee a successful configure IF THE MaxPak III DRIVE IS OFF-LINE.

**REGISTER 44** – (Total output integer registers) This value represents the number of output integers the MaxPak III drive has defined in its HSL register map. It is provided so the user may read this register and determine the largest value permitted in REGISTER 75 that will guarantee a successful configure. The value in this register is the maximum value allowed in REGISTER 75 regardless of the current state of the MaxPak III drive (on or off line).

**REGISTER 45** – (Total output boolean bits) This value represents the number of output booleans the MaxPak III drive has defined in its HSL register map. It is provided so the user may read this register and determine the largest value permitted in REGISTER 76 that will guarantee a successful configure. The value in this register is the maximum value allowed in REGISTER 76 regardless of the current state of the MaxPak III drive (on or off line).

**REGISTER 60** – (Fatal Error #) A Reliance Service register. Contains specific fatal error codes used in board diagnostics, repair, and replacement.

REGISTER 62 & 63 - (HSL Comm Card ASCII ID 'HSL ') Card Ascii ID.

**REGISTER 64** – Contains the software revisions of the HSL module. This data is sent to the MaxPak III drive when the link is established. This verifies that the software revision of the MaxPak III drive and the software revision of the HSL module are compatible.

**REGISTER 70** – (Number of integer registers to transmit to the MaxPak III drive). This register may be changed at any time, although the change will not take effect until a configure command is issued with the drive stopped (SEQ\_ARM\_ACTIVE@ = OFF). The number specified in REGISTER 70 includes the high priority register (Register 1100). For example, if an application wanted to send REGISTERS 1100 – 1109 then REGISTER 70 should contain 10. If the range is exceeded, the value will remain as the application has configured it (out of range), and REGISTER 27 bits 15 and bit 3 or 5 will be set to 1 to indicate a configuration error.

Note: No other messages with the exception of a configure may be sent when REGISTER 27 is non-zero.

DEFAULT VALUE = 2. MAX. RANGE = 2 to 256.

Note: The actual range is limited by the MaxPak III drive variable map.

**REGISTER 71** – (Number of boolean bits to transmit to the MaxPak III drive.) The user may change this register any time. The user must insure SEQ\_ARM\_ACTIVE@ is OFF and then send a configure command to the MaxPak III drive before changes in this register will have any effect. If the range is exceeded, the value will remain as the application has configured it (out of range), no messages will be sent to the MaxPak III drive, and REGISTER 27 bits 15 and bit 4 or 5 will be set to 1 to indicate a configuration error.

DEFAULT VALUE = 2. MAX. RANGE = 2 to 256.

Note: The actual range is limited by the MaxPak III drive variable map.

**REGISTER 75** – (Number of On-Line integer registers to receive from the MaxPak III). This register may be changed at any time, although the change will not take effect until a configure command is issued with the drive stopped (SEQ\_ARM\_ACTIVE@ = OFF). Use COMMAND REGISTER 30 to send commands to the MaxPak III drive. The number specified in REGISTER 75 includes the two high priority registers (100 and 101). For example, if an application wanted to receive REGISTERS 100 – 109, then REGISTER 75 should contain a 10. If the range is exceeded, the value will remain as the application has configured it (out of range), no messages will be sent to the MaxPak III drive, and REGISTER 27 bits 15 and bit 0 or 5 will be set to 1 to indicate a configuration error.

DEFAULT VALUE = 2. RANGE = 2 to 256.

Note: The actual range is limited by the MaxPak III drive variable map.

**REGISTER 76** – (Number of On-Line boolean registers to receive from the MaxPak III drive). The user must insure SEQ\_ARM\_ACTIVE@ is OFF and then send a configure command to the MaxPak III drive before changes in this register will have any effect. If the range is exceeded, the value will remain as the application has configured it (out of range), no messages will be sent to the MaxPak III drive, and REGISTER 27 bits 15 and bit 1 or 5 will be set to 1 to indicate a configuration error.

DEFAULT VALUE = 2. MAX. RANGE = 2 to 256.

**Note:** The actual range is limited by the MaxPak III drive variable map.

**REGISTER 80** – (Maximum receive TIMEOUT value) Specifies the maximum time (in milliseconds) from the last valid message that the HSL module will wait for a message from the MaxPak III drive before a timeout error will occur. The user must insure SEQ\_ARM\_ACTIVE@ is OFF and then send a configure command to the MaxPak III drive before changes in this register will have any effect. Use COMMAND REGISTER 30 to send it. If the valid range is exceeded, the value will remain as was originally configured, no messages will be sent to the MaxPak III drive, and REGISTER 27 bits 15 and 5 will be set to 1 to indicate a configuration error.

DEFAULT VALUE = 45msec. (2 x L2\_SCAN\_PERIOD% + 5msec) RANGE = 10 to 100 msec. **REGISTER 81** – (Message Scan period) Specifies the tick interval between update requests (e.g. speed loop ticks). Note: 1 tick = 0.5ms. The user must insure SEQ\_ARM\_ACTIVE@ is false and then send a configure command to the MaxPak III drive before changes in this register will have any effect. If the range is exceeded, the value will remain as the application has configured it (out of range), no messages will be sent to the MaxPak III drive, and REGISTER 27 bit 15 and possibly bit 5 will be set to 1 to indicate a configuration error.

DEFAULT VALUE = 11. RANGE = 11 to 198 ticks (5.5 msec to 99 msec).

# 2.2.2 MaxPak III High Speed Link (HSL) Variables

# HSL\_TIMEOUT\_T%

| Description:<br>Type: | HSL receive message timeout time period in msec<br>Input Variable |

|-----------------------|-------------------------------------------------------------------|

| Retentive:            | Yes                                                               |

| Access Level:         | 5                                                                 |

| Value Range:          | 10 to 250                                                         |

| Scale:                | 1 = 1 millisecond                                                 |

| Typical Value:        | $54 = (2 \times AutoMax DCS Scan Period) + 10$                    |

| Comments:             | Maximum time between valid messages received by                   |

|                       | the MaxPak III drive from the 57C424 (HSL module)                 |

|                       | after a connection between them has been                          |

|                       | established. If this time is exceeded,                            |

|                       | HSL_TIMEOUT_E@ is set to ON. The timeout                          |

|                       | function cannot be disabled when the MaxPak III                   |

|                       | drive is on-line.                                                 |

# HSL\_ENABLE@

| Description:   | HSL communications channel enable configuration switch.                                                                                                                                            |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре:          | Input Variable                                                                                                                                                                                     |

| Retentive:     | Yes                                                                                                                                                                                                |

| Access Level:  | 4                                                                                                                                                                                                  |

| Value Range:   | ON, OFF                                                                                                                                                                                            |

| Typical Value: | OFF                                                                                                                                                                                                |

| Comments:      | If ON during a MaxPak III drive power-up or                                                                                                                                                        |

|                | OFF-LINE to ON-LINE transition, the HSL                                                                                                                                                            |

|                | communications channel is installed as the controller<br>of the MaxPak III drive onboard serial port (provided<br>MB_ENABLE@ = OFF). When OFF, the HSL<br>communications channel is not installed. |

# HSL\_XMITD\_MSGS%

| Description:   | Number of HSL messages transmitted by the                                                                                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | MaxPak III drive                                                                                                                                                                                                |

| Туре:          | Output Variable                                                                                                                                                                                                 |

| Retentive:     | No                                                                                                                                                                                                              |

| Access Level:  | 0                                                                                                                                                                                                               |

| Value Range:   | -32768 to 32767                                                                                                                                                                                                 |

| Scale:         | N/A                                                                                                                                                                                                             |

| Typical Value: | -32768 to 32767                                                                                                                                                                                                 |

| Comments:      | This variable is treated as an unsigned number by the MaxPak III drive. It therefore starts at zero (0), counts to 32767, rolls over to -32768, and continues counting towards zero (0). Its primary use is for |

|                | diagnostics.                                                                                                                                                                                                    |

# HSL\_RECVD\_MSGS%

| Description:   | Number of HSL messages received by the<br>MaxPak III drive                                                                                                                                                                   |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type:          | Output Variable                                                                                                                                                                                                              |

| Retentive:     | No                                                                                                                                                                                                                           |

| Access Level:  | 0                                                                                                                                                                                                                            |

| Value Range:   | -32768 to 32767                                                                                                                                                                                                              |

| Scale:         | N/A                                                                                                                                                                                                                          |

| Typical Value: | -32768 to 32767                                                                                                                                                                                                              |

| Comments:      | This variable is treated as an unsigned number by the MaxPak III drive. It therefore starts at zero (0), counts to 32767, rolls over to -32768, and continues counting towards zero (0). Its primary use is for diagnostics. |

# HSL\_CHKSUM\_ERRS%

| Description:<br>Type: | Number of HSL message checksum errors<br>Output Variable                                                                                                                                                                                                                                                                                                                        |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Retentive:            | No                                                                                                                                                                                                                                                                                                                                                                              |

| Access Level:         | 0                                                                                                                                                                                                                                                                                                                                                                               |

| Value Range:          | -32768 to 32767                                                                                                                                                                                                                                                                                                                                                                 |

| Scale:                | N/A                                                                                                                                                                                                                                                                                                                                                                             |

| Typical Value:        | -32768 to 32767                                                                                                                                                                                                                                                                                                                                                                 |

| Comments:             | A checksum error indicates a corrupted message has<br>been received. The contents of a message with a<br>checksum error are discarded. This variable is treated<br>as an unsigned number by the MaxPak III drive. It<br>therefore starts at zero (0), counts to 32767, rolls over<br>to -32768, and continues counting towards zero (0).<br>Its primary use is for diagnostics. |

.

# HSL\_TIMEOUT\_E@

| Description:<br>Type:<br>Retentive:<br>Access Level:<br>Value Range:<br>Typical Value:<br>Comments: | HSL receive message timeout error status<br>Output variable<br>No<br>O<br>ON or OFF<br>OFF<br>ON if the MaxPak III drive detects a receive message<br>timeout condition. A receive message timeout<br>condition occurs when the MaxPak III drive does not<br>receive a new update message within the receive<br>timeout period (HSL_TIMEOUT_T% msec) since the<br>last update message was received. This condition<br>forces a re-connection between the HSL module and<br>the MaxPak III drive. One the receive time output the |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                     | forces a re-connection between the HSL module and<br>the MaxPak III drive. Once the re-connection has<br>been established, HSL_TIMEOUT_E@ is set to OFF.                                                                                                                                                                                                                                                                                                                                                                         |

# HSL\_XOVRLAP\_E@

| Description:   | HSL transmit message overlap error status                                                                                                                                                                                                                                                           |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type:          | Output variable                                                                                                                                                                                                                                                                                     |

| Retentive:     | No                                                                                                                                                                                                                                                                                                  |

| Access Level:  | 0                                                                                                                                                                                                                                                                                                   |

| Value Range:   | ON or OFF                                                                                                                                                                                                                                                                                           |

| Typical Value: | OFF                                                                                                                                                                                                                                                                                                 |

| Comments:      | ON if the MaxPak III drive is in a transmit overlap<br>condition, OFF otherwise. A transmit message<br>overlap condition occurs when the MaxPak III drive is<br>currently sending a message and the<br>L2_SCAN_PERIOD% expires, causing the MaxPak III<br>drive to attempt to send another message. |

# HSL\_ROVRLAP\_E@

| Description:<br>Type:<br>Retentive:<br>Access Level:<br>Value Range:<br>Typical Value:<br>Comments: | Dynamic Receive Overlap Error Detection Flag<br>Output variable<br>No<br>0<br>ON or OFF<br>OFF<br>ON if the MaxPak III drive detects a receive message<br>overlap condition. A receive message overlap<br>condition occurs when the MaxPak III drive receives<br>a message before the previous received message<br>has been processed. This condition forces a<br>reconnection between the HSL module and the<br>MaxPak III drive. Once the re-connection has been |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

.

# FLT\_HSL\_COMM\_L@

| Access Level:       0         Value Range:       ON or OFF         Scale:       Boolean         Typical Value:       OFF         Comments:       Latched (ON) when any of HSL_TIMEOUT_E@,<br>HSL_ROVRLAP_E@, or HSL_XOVRLAP_E@,<br>become ON while the MaxPak III drive is On-Line.<br>Unlatched (OFF) by a drive fault reset command (A | Value Range:<br>Scale:<br>Typical Value: | ON or OFF<br>Boolean<br>OFF<br>Latched (ON) when any of HSL_TIMEOUT_E@,<br>HSL_ROVRLAP_E@, or HSL_XOVRLAP_E@,<br>become ON while the MaxPak III drive is On-Line.<br>Unlatched (OFF) by a drive fault reset command (An<br>off-to-on transition of FLT_RESET@). This variable is<br>also contained in bit 10 of the variable |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

## HSL\_ERROR\_FLAGS%

| Description:   | HSL communications error flags            |

|----------------|-------------------------------------------|

| Type:          | Output Variable                           |

| Retentive:     | No                                        |

| Access Level:  | 0                                         |

| Value Range:   | 0 to 7                                    |

| Scale:         | N/A                                       |

| Typical Value: | 0 (no errors)                             |

| Comments:      | Contains the variables:                   |

|                | HSL_TIMEOUT_E@ in bit 0                   |

|                | HSL_ROVRLAP_E@ in bit 1                   |

|                | HSL_XOVRLAP_E@ in bit 2                   |

|                | Bits $3 - 15$ are not used and will be 0. |

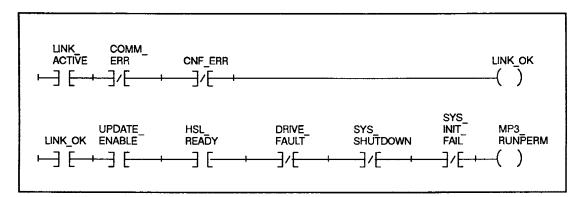

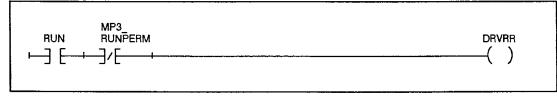

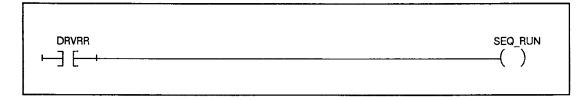

# 2.2.3 Sequence of Events

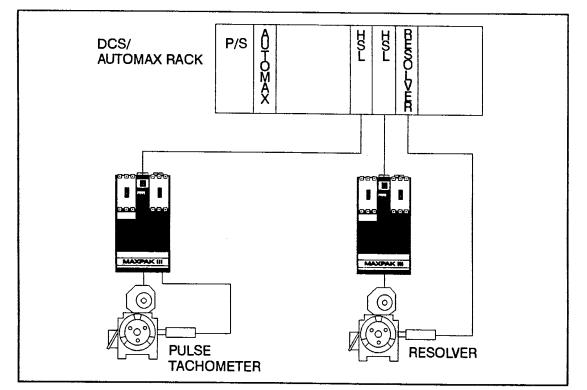

The HSL module can transmit many variables. One variable from AutoMax to the MaxPak III drive has high priority and 2 variables from the MaxPak III drive to the AutoMax have high priority. The high priority variables are typically used by current reference and sometimes speed feedback. The following diagram shows "TYPICAL" MaxPak III-toAutoMax connections.

Figure 2-2 - Typical MaxPak III-to-AutoMax Connections

The "TYPICAL" sequence of events is as follows:

If speed feedback is connected directly to the MaxPak III drive, the AutoMax DCS processor runs the Speed Loop, generates a current reference, and sends the current reference via HSL module to the MaxPak III drive. The MaxPak III drive uses this reference for input to the Current Minor Loop. Speed feedback is then sent back to the AutoMax DCS from the MaxPak III drive. Upon receipt of speed feedback, the HSL module will interrupt the AutoMax thereby starting its speed loop. In this case, the MaxPak III drive has both speed feedback and armature voltage locally, and may act immediately if a problem is detected (i.e., tachloss and overspeed).

Reference section 2.2.6 of this instruction manual for details on tach loss and overspeed.

# 2.2.4 MESSAGES

Many messages may be sent to the MaxPak III drive and are controlled by command REGISTER 30 in the AutoMax DCS. When the AutoMax DCS task is ready to send data, it must command the HSL module via dual-port REGISTER 30 to begin sending the message.

The MaxPak III drive continually sends a new message to the AutoMax DCS at the end of each MaxPak III L2\_SCAN\_PERIOD%. L2\_SCAN\_PERIOD% is a user configurable variable typically equal to 20 mSec. The number of registers that are sent from each end of the link is user configurable at both ends, independently. The message size is controlled by the driver software, but is directly related to the HSL module's message scan period (e.g. speed loop ticks in Register 81) and MaxPak III drive's L2\_SCAN\_PERIOD% value.

# 2.2.4.1 Message Control (L2\_SCAN\_PERIOD%)

The messages sent from the AutoMax DCS to MaxPak III drive and from the MaxPak III drive to AutoMax DCS are not necessarily synchronized.

Update time (scan time) to transmit variables from the MaxPak III drive to the HSL module is based on the time set into the MaxPak III drive variable L2\_SCAN\_PERIOD% (10 - 20 milliseconds). (Note: A value of 5 msec for L2\_SCAN\_PERIOD% is not supported for use with the HSL.) Programmable timeout periods on both the MaxPak III drive and HSL module are employed to assure valid data and link integrity.

## 2.2.4.1.1 AutoMax DCS to MaxPak III Information Update Rate Calculations

#### WARNING

THE USER MUST INSURE THAT ALL APPLICATION CRITICAL PARAME-TERS (VARIABLES) ARE UPDATED SUFFICIENTLY OFTEN FOR SAFE AND PROPER OPERATION (E.G SPEED FEEDBACK, VOLTAGE FEEDBACK, AND E-STOP). CRITICAL PARAMETERS MUST BE GIVEN HIGH PRIORITY OR FIXED REGISTER ASSIGNMENTS AND UPDATE TIMES MUST BE CALCU-LATED. FAILURE TO OBSERVE THIS PRECAUTION COULD RESULT IN BODILY INJURY.

The time required for the HSL module to send a message to the MaxPak III drive is determined by the message type. An update command will be recognized within 600 usec of the command being written to Register 30. A request to place the MaxPak III drive on-line/off-line or a configure request will take longer (maximum of 11 ms).

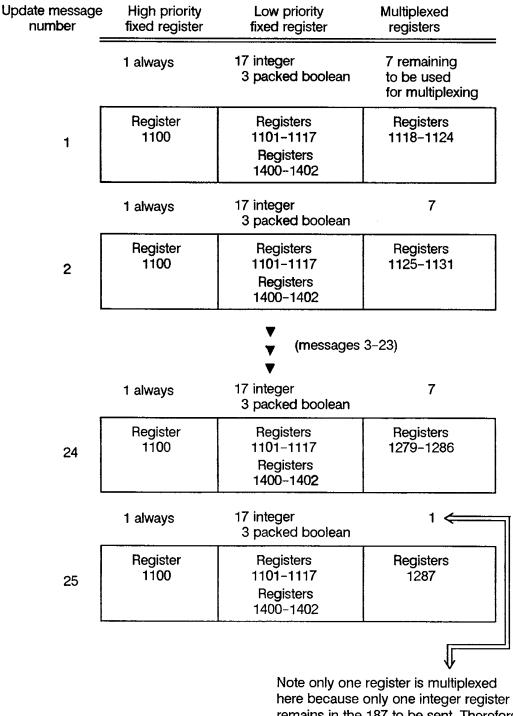

Each update command causes a portion of the output integer map (Registers 1100 - 1355) and a portion of the output boolean map (Register 1400-1415) to be sent to the MaxPak III drive. Some of these variables are "fixed", meaning that they will be sent each time an update request is issued. The "high priority" register is included in this category. Other variables are "multiplexed", meaning that they will be distributed over several update messages and thus may take longer to transmit. Once all multiplexed variables have been sent, the cycle repeats, starting with the current value of the first multiplexed variable. The number of fixed integers and booleans, and the total number of registers per update message are determined by the tick count written in Register 81. Fixed integers are contiguous, starting with Register 1100 and fixed booleans are contiguous, starting with Register 1400. A table detailing message composition for varying tick rates and calculations for determining information update rates follow (also see Section 4.5).

Optional synchronization of the AutoMax DCS speed loop task to the MaxPak III L2\_SCAN\_PERIOD% is provided via Multibus interrupt. The interrupt occurs when the AutoMax DCS has received the two high priority integer registers from the MaxPak III drive.

| Reg 81<br>(TICKS) | (1) Max # Fixed<br>Integer (MFI)<br>Registers | (2) Max # Fixed<br>Boolean (MFB)<br>Registers | Max # of<br>Registers per<br>Message (MRPM) |

|-------------------|-----------------------------------------------|-----------------------------------------------|---------------------------------------------|

| 11-21             | 2                                             | 1                                             | 4                                           |

| 22-32             | 6                                             | 2                                             | 10                                          |

| 33-43             | 9                                             | 3                                             | 17                                          |

| 44-54             | 18                                            | 3                                             | 28                                          |

| 55-65             | 18                                            | 3                                             | 38                                          |

| 66-76             | 18                                            | 3                                             | 46                                          |

| 77-87             | 21                                            | 3                                             | 55                                          |

| 88-98             | 29                                            | 4                                             | 64                                          |